## **Cronfa - Swansea University Open Access Repository**

| This is an author produced version of a paper published in:  Nano Energy                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cronfa URL for this paper: http://cronfa.swan.ac.uk/Record/cronfa38751                                                                                                                           |

| Paper: Nie, J., Hu, G., Li, L. & Zhang, Y. (2018). Piezotronic Analog-To-Digital Converters Based on Strain-gated Transistors. <i>Nano Energy</i> http://dx.doi.org/10.1016/j.nanoen.2018.02.034 |

| Released under the terms of a Creative Commons Attribution Non-Commercial No Derivatives License (CC-BY-N<br>ND).                                                                                |

| This item is brought to you by Swansea University. Any person downloading material is agreeing to abide by the                                                                                   |

This item is brought to you by Swansea University. Any person downloading material is agreeing to abide by the terms of the repository licence. Copies of full text items may be used or reproduced in any format or medium, without prior permission for personal research or study, educational or non-commercial purposes only. The copyright for any work remains with the original author unless otherwise specified. The full-text must not be sold in any format or medium without the formal permission of the copyright holder.

Permission for multiple reproductions should be obtained from the original author.

Authors are personally responsible for adhering to copyright and publisher restrictions when uploading content to the repository.

http://www.swansea.ac.uk/library/researchsupport/ris-support/

# Author's Accepted Manuscript

Piezotronic Analog-To-Digital Converters Based on Strain-gated Transistors

Jiaheng Nie, Gongwei Hu, Lijie Li, Yan Zhang

www.elsevier.com/locate/nanoenergy

PII: S2211-2855(18)30102-2

DOI: https://doi.org/10.1016/j.nanoen.2018.02.034

Reference: NANOEN2521

To appear in: Nano Energy

Received date: 31 January 2018 Revised date: 15 February 2018 Accepted date: 15 February 2018

Cite this article as: Jiaheng Nie, Gongwei Hu, Lijie Li and Yan Zhang, Piezotronic Analog-To-Digital Converters Based on Strain-gated Transistors, *Nano Energy*, https://doi.org/10.1016/j.nanoen.2018.02.034

This is a PDF file of an unedited manuscript that has been accepted for publication. As a service to our customers we are providing this early version of the manuscript. The manuscript will undergo copyediting, typesetting, and review of the resulting galley proof before it is published in its final citable form. Please note that during the production process errors may be discovered which could affect the content, and all legal disclaimers that apply to the journal pertain.

# Piezotronic Analog-To-Digital Converters Based on Straingated Transistors

Jiaheng Nie<sup>1</sup>, Gongwei Hu<sup>1</sup>, Lijie Li<sup>2</sup>, Yan Zhang<sup>1,3,4,\*</sup>

<sup>1</sup>School of Physics, School of Physical Electronics, University of Electronic Science and Technology of China, Chengdu 610054, China

<sup>2</sup>Multidisciplinary Nanotechnology Centre, College of Engineering, Swansea University, Swansea, SA1 8EN, UK

<sup>3</sup>Beijing Institute of Nanoenergy and Nanosystems, Chinese Academy of Sciences, Beijing 100083, China

<sup>4</sup>College of Nanoscience and Technology, University of Chinese Academy of Sciences, Beijing 100049, China

#### **Abstract**

We report a novel approach to achieve piezotronic analog-to-digital converters (ADCs) based on strain gated transistors (SGTs). A single SGT can act as voltage converter, comparator, and amplifier. The new piezotronic ADC devices benefit from high sensitivity of the piezotronic SGT responding to the external strains. This design can significantly reduce the power consumption and the size of these devices, which are considered as crucial factors in self-powered systems. The fundamental concept of the device design has been demonstrated by three piezotronic ADC architectures formed by various networks comprised of SGTs and resistors. Analog-to-digital conversion and logic operations of these piezotronic ADCs blocks are analyzed and logic truth tables for all those configurations are presented. This design has immense potential for enormous applications in future human-machine interfaces, internet of things, and sensor networks.

**Keywords:** piezotronics; strain-gated transistor; piezotronic Analog-To-Digital Converter; piezotronic logic device; strain mapping

#### 1. Introduction

<sup>\*</sup>To whom correspondence should be addressed; zhangyan@uestc.edu.cn

Piezotronics and piezophototronics [1, 2] have attracted tremendous interests in the self-powered technology, [3] pervasive computing, [4, 5] and sensors [6]. Carrier transport characteristics of nanodevices can be controlled by strain-induced piezoelectric charges [7]. Recently, a series of novel devices have been obtained based on piezoelectric semiconductor materials in multifunction logic computing, [8] biomedical sensors, [9] ultra-high sensitivity strain sensors, [10] piezoelectric field effect transistor, [11] piezophototronic LEDs, [12, 13] and solar cell [14]. Piezotronic and piezo-phototronic array strain mapping devices have obtained significant attention for the applications in the new emerging field of flexible electronics and parallel optical signal processing [15, 16].

Piezotronic logic elements have become very promising for future applications in direct detecting, processing, and control of the external environmental stimuli. Based on the high-sensitivity strain-gated transistors, piezotronic logic devices can be fabricated by using ZnO nanowires (NWs) for the basic logical operations such as NAND, NOR, and XOR [4]. Piezo-phototronic binary computation has also been reported by using wurtzite structure ZnO and CdS [8]. Coupling of piezoelectric, semiconductivity and optical characteristics plays a key role to convert the mechanical or optical stimuli to ON or OFF output signals in piezoelectric logical devices.

Strain mapping and digital processing need the conversion from a continuous-time and continuous-amplitude analog signal to a discrete-time and discrete-amplitude digital signal. Piezotronic transistors act not only as strain sensors, but also as signal comparators and amplifiers. These properties offer novel piezotronic analog-to-digital converters (ADCs). Due to the high-sensitivity and low-power consumption properties, the strain-gated transistors (SGTs) are promising candidates for flexible and low-power piezotronic ADCs. The strain sensitivity (gauge factor) of SGTs can reach up to 1250, which is higher than Si-doped and carbon nanotubes strain sensor [6]. Furthermore, the energy consumption of the nanowire devices is in the order of pW, which can be regarded as zero power consumption [17]. SGTs can also exhibit ultra-fast response time because the device size is in the nanoscale. Therefore, the piezoelectric logic device based on SGTs can be a fundamental component of electronic circuits, with prominent characteristics of high-sensitivity, ultra-low power consumption and fast response time.

In this manuscript, the basic principle of piezotronic analog-to-digital converter based on SGTs has been demonstrated. Three design approaches are proposed by using the piezotronic effect. First type is structured by using various SGTs with different current-voltage characteristics, which can be obtained by various piezoelectric materials or with energy band engineering. To simplify the device fabrication, second type is using various resistors and SGTs with the same

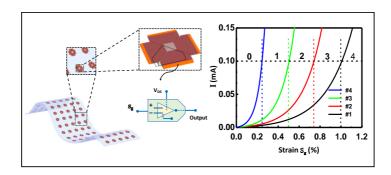

current-voltage characteristics. These two types of piezotronic ADCs can realize ultra-low power consumption with reduced number of components. The third type is the assembly of piezotronic transistor-based strain sensors and conventional ADCs for the purpose of comparison with above two new designs. Take the first type as an example, the schematic diagram is illustrated in Figure 1. Piezotronic ADC devices are inserted into the flexible substrate, forming large-scale piezotronic ADCs arrays for detecting the external strain, as shown in Figure 1(a). Figure 1(b) shows the enlarged image of four piezotronic ADCs, and the basic structure of a single piezotronic ADC device consists of four branched SGTs that can achieve 2-bit output of strain signals. Figure 1(c) shows the circuit symbol and equivalent circuit of each branch based on SGT series circuit. Figure 1(d) shows the circuit diagram, which has N SGT branches. Piezotronic ADCs have enormous potential applications for strain imaging, man-machine interface, artificial intelligence and analog computing.

## 2. Basic Principle of Piezotronic Analog-to-Digital Converter

The basic block unit of a piezotronic ADC is the SGT acting as the strain-voltage converter, the comparator and amplifier. When the electrical current exceeds a certain threshold, the SGT will change from OFF state to ON state, corresponding to digital output signals 0 and 1, respectively. The strain threshold can be different by choosing SGTs with different current-voltage characteristics. Various SGTs with diverse I-V characteristics produced by various routines can form ADC devices responding to different external strains. Thus, the strains with different amplitude intervals can be encoded to different digital output signals. Therefore, the ADC devices fabricated from SGTs of N breaches will convert a tensile or compressible strain signal to digital information.

For a single SGT with a fixed bias voltage  $V_D$ , the current density can be given by [7]

$$J = J_0 \cdot \exp\left(\frac{qe_{33}s_{33}W_{piezo}}{2\varepsilon_s kT}\right) \left[\exp\left(\frac{q V_D - V_{out}}{kT}\right) - 1\right]$$

(1)

where  $J_0$  is the saturation current density, q is the absolute value of an electron charge,  $e_{33}$  is the piezoelectric coefficient,  $s_{33}$  is the applied strain along the grown direction,  $s_{0i}$  is the width of piezoelectric charge distribution,  $s_{3}$  is dielectric constant,  $s_{3}$  is Boltzmann constant and  $s_{3}$  is the temperature,  $s_{0i}$  denotes the output voltage.

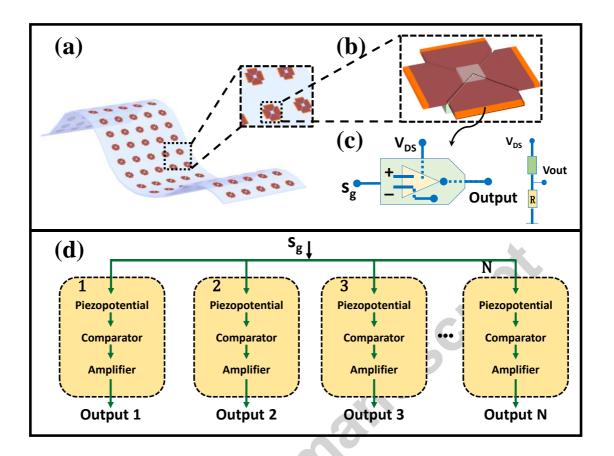

The voltage on a resistor can be obtained from a piezoelectric transistor and resistor series circuit. Figure 2 shows the output voltage  $V_{out}$  and voltage sensitivity  $dV_{out}/ds_g$  as a function of

strain  $s_g$  varying from 0 to 10%. Figure 2(a) and (d) show that the output voltage  $V_{out}$  increases with the increasing strain  $s_g$  for a fixed resistor  $R = 1 \text{ k}\Omega$  and drain voltage  $V_D$  ranges from 1 V to 7 V. The sensitivity of SGT  $dV_{out}/ds_g$  is approximatively constant at small strains, for example, less than 3% of strain at  $V_D = 1$  V, and it increases with the drain voltage  $V_D$ . Figure 2(b) and (e) also exhibit output voltage  $V_{out}$  and sensitivity  $dV_{out}/ds_g$  with strain  $s_g$  at the fixed drain voltage  $V_{\scriptscriptstyle D}=$  2 V , while resistor R varies from 10 k $\Omega$  to 150 k $\Omega$  . Output voltage  $V_{out}$  increases with the strain and reaches up to 2.0 V. The sensitivity can be higher when R is smaller. The sensitivity deceases from 1.8 to 0 with increasing strain. Furthermore, the output properties of piezotronic transistor significantly depend on the piezoelectric materials as shown in Figure 2(c) and (f). The output voltage and sensitivity of the piezotronic transistors based on ZnO, GaN and InN are plotted as a function of strain for fixed R = 1 M $\Omega$  and drain voltage  $V_D$  = 2 V. ZnO piezotronic transistor has higher output voltage and sensitivity compared to GaN and InN for strain ranging from 0 to 4.5%. In our calculations, piezoelectric constants  $e_{33}$  for ZnO, [18] GaN, InN are 1.22, 0.73, and 0.97 C/m² respectively. [19] Dielectric constants  $\varepsilon_s$  are 8.91, [18] 10.4, and 14.6 respectively. [19] Although we use the ideal piezotronic junction model to demonstrate the general principle of piezotronic ADCs, the  $V_{out}$  variation can significantly increase by controlling the sensitivity of the SGT. In practice, the  $V_{out}$  can change from 0 V to 0.975 V at drain-source voltage of 1.0 V in previous experiments. [4]

For a *K*-bits piezotronic ADC, strain resolution (Res) is an important factor and can be obtained by uniformly dividing the strain region, which is given by [20]

$$Res = \frac{s_0}{s_m} = \frac{s_0}{2^K s_0} = \frac{1}{2^K}$$

(2)

where  $N=2^K$ ,  $s_0$  is strain interval,  $s_m$  is maximum value of strain and equals to  $2^K s_0$ . Res is expressed by K instead of  $1/2^K$ .

The conversion error coefficient from strain signal to digital signal should satisfy the relation [20]

$$\delta \le \frac{1}{2} LSB \tag{3}$$

where LSB equals to  $S_0$ .

e t is noise signal with T, sampling interval, equaling  $1/f_{sample}$ . [20]

$$e \ t = Q\left(\frac{t}{T} - \frac{1}{2}\right) \tag{4}$$

where Q is the size of the elementary quantization step, which is equivalent to LSB.

Mean value of noise power spectrum within a certain T was derived by [20]

$$NP_{o} rms = \sqrt{\frac{1}{T}} \int_{0}^{T} e^{-t} t^{-2} dt = \sqrt{\frac{1}{T}} \int_{0}^{T} \left[ Q \left( \frac{t}{T} - \frac{1}{2} \right) \right]^{2} dt = \frac{Q}{\sqrt{12}}$$

(5)

To summarize, signal to noise ratio, SNR (in dB) is given by the equation (6) in piezotronic ADCs.  $s_m$  are all values included in the upper and lower bounds, which demonstrates the full-scale strain range [20].

$$SNR \ dB = 20 \cdot \log_{10} \left( \frac{s_m \ rms}{NP_0 \ rms} \right)$$

(6)

The ideal sinusoidal input analog signal is used in this paper to further characterize piezotronic ADC's SNR property. In this condition, SNR is linear in the resolution K [20].

$$SNR \ dB = 20 \cdot \log_{10} \left( \frac{s_m}{2\sqrt{2}} \cdot \frac{1}{\frac{s_m}{2^K \sqrt{12}}} \right) = 6.02 \cdot K + 1.76$$

(7)

#### 3. Piezotronic Analog-To-Digital Converters Based on strain-gated transistors

Take piezotronic ADCs based on four SGTs as example, three piezotronic ADC architectures can be designed using the basic principle. The first two piezotronic ADCs have few electronic elements, which are beneficial to reduce power consumption. The functions of all three types of piezotronic ADCs are identical. The minimum interval  $s_0$  of three piezotronic ADC is 0.25%, and strain resolution (Res) is  $s_0/s_m = 1/2^\kappa$ . SNR (=13.8 dB) is employed to achieve a better interpretation of ADC performance limits, where we choose ideal sine signal and noise from sampling error without influence of materials characteristics and external noise.

#### 3.1 Piezotronic ADCs based on strain-gated transistors and fixed resistors

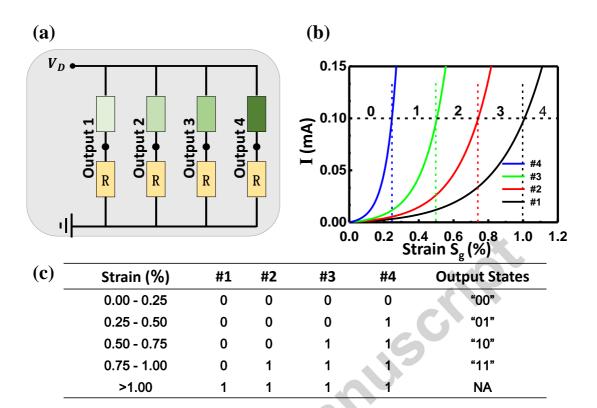

Piezotronic transistors based on various materials or techniques can result in different output

responses to externally applied strains. Figure 3(a) shows the schematic diagram of piezotronic ADCs by using four strain-gated transistors connected with four fixed resistors parallelly to obtain digital signal of the strain value. Each SGT has different current-strain characteristics as shown in Figure 3(b). Branch SGT #4 has highest sensitivity and thus will be firstly switched to ON state for small strain of 0.25% with the threshold current of 0.1 mA. When the strain increases, the branch SGT #3, #2 and #1 can be switched on at strains of 0.5%, 0.75% and 1.00%. There are four basic signal output states for the strain varying from 0 to 1.00%. The logic signal of the ADCs outputs "00" for strain less than 0.25%. While strain is within the region 1 (0.25%  $\sim$ 0.5%), only branch SGT #4 is switched on and the output signal is "01". Signal state "10" is output for the strain in region 2 (0.5% ~ 0.75%) for which branch SGT #4 and #3 are in ON state and branch SGT #2 and #1 are in OFF state. While the branch SGT #4, #3 and #2 are simultaneously switched on and branch SGT #1 is switched off for the strain in region 3, "11" signal occurs. In this design, branch SGT #1 is used for overflow test. While the strain is higher than 1.00%, the branch SGT #1 has the output "1", thus, all of branch are switched on. This is overflow state, which indicates the strain reach the upper limit of measurement of this piezotronic ADC. The generated four logic units "00", "01", "10" and "11" can be used for the further encoder.

Piezotronic ADCs based on four parallel SGTs exhibit excellent performance compared to conventional ADCs. For instance, the comparator and the amplifier can be realized by a single piezotronic ADC. This principle can be also used in integrated resistance network by parallelly connecting different SGT circuits, giving rise to multifunctionality of assembled units. Piezotronic ADCs offer a unique method for strain-to-digital conversion by eliminating the comparator network, which can be used to reduce the number of elements and simplify conversion steps. Thus, this design leads to very low power consumption.

#### 3.2 Piezotronic ADCs based on strain-gated transistors and various resistors

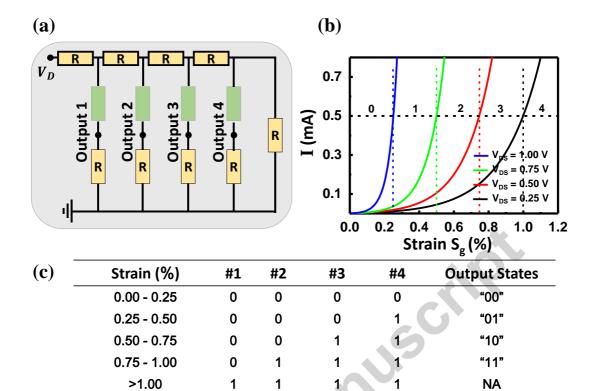

Figure 4(a) shows the schematic of second type piezotronic ADC based on the same SGT and various resistors. This design principle can simplify the device fabrication. With applied strain, drain voltage of each SGT is different, resulting in different current outputs. The source-drain voltage can be fixed at a constant value for each SGT by properly adjusting the resistor value. Figure 4(b) shows the output current as a function of the strain for fixed source-drain voltages of  $V_{DS} = 1$  V, 0.75 V, 0.5 V, and 0.25 V, respectively. Four logic states, "00", "01", "10" and "11" are generated while the strain changes from 0% to 1.00%. When the threshold current is set at 0.5 mA, the logic value is "00" state for the strain 0% - 0.25% at the threshold current of

0.5 mA. All SGTs are in OFF states at this condition, as shown in Figure 4(c). The first SGT being at ON state corresponds to the maximum source-drain voltage  $V_{DS} = 1$  V for the strain varying in 0.25% - 0.5%, leading to "01" logic state. With the strain increases to 0.5% - 0.75, the second SGT is also at ON state and the logic state is "10". The third SGT starts to open and logic state "11" is generated for the strain range of 0.75% - 1.00%.

#### 3.3 Piezotronic ADCs based on single strain-gated transistors

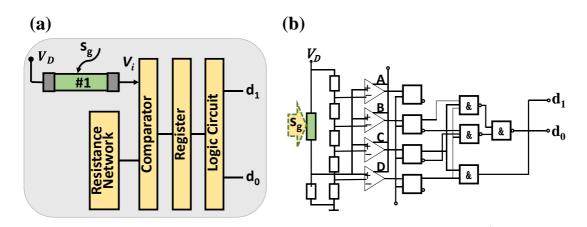

For comparison, SGT acts as a strain sensor, which can be directly connected with conventional ADCs based on silicon chip. The design schematic is shown in Figure 5. When a bias voltage is added on piezoelectric transistor, the strain-induced piezoelectric potential will change the output voltage  $V_i$ . There is a comparator circuit of rated voltage for four resistors divider, resulting in reference voltages with various levels. Logic value "1" is generated when  $V_i$  is higher than the threshold level of the comparator. Logic value "0" is generated when  $V_i$  is less than the threshold level of the comparator. The output logic value from the comparator is transferred to the registers and used for next logic computations. The output terminal of the register connected to the gate logic circuit for the truth table of the strain signal, as shown in Figure 5(c).

#### 4. Summary

Piezotronic ADCs can be used to convert external strain value to logic bit by using various circuit architectures with strain-gated transistors. There are three proposals to design piezotronic ADCs: the first two are using strain-gated transistors but with fixed resistors and with various resistors. The third one is based on single strain-gated transistors. The logic states can be obtained by comparing the output current with a threshold value under the external strain. The logic truth table is presented as a key parameter relating the strain signal to the logic bit. Based on the logic operation principle, piezotronic ADC can be further employed into high-sensitivity devices to achieve identification and measurement of external information synchronously. This study not only provides a theoretical insight into the design of novel ADCs, but also has wider potential applications for human–electronics interfacing and nanoelectromechanical systems.

#### Acknowledgements

The authors are thankful for the support from University of Electronic Science and Technology of China (ZYGX2015KYQD063), Swansea University, SPARC II project, and

Thousand Talents program for a pioneer researcher and his innovation team, China.

#### Reference

- [1] W. Wu, Z.L. Wang, Nature Reviews Materials, 1 (2016).

- [2] Z.L. Wang, Nano Today, 5 (2010) 540-552.

- [3] S. Xu, Y. Qin, C. Xu, Y. Wei, R. Yang, Z.L. Wang, Nat Nanotechnol, 5 (2010) 366-373.

- [4] W. Wu, Y. Wei, Z.L. Wang, Adv Mater, 22 (2010) 4711-4715.

- [5] J. Song, Y. Zhang, C. Xu, W. Wu, Z.L. Wang, Nano Letters, 11 (2011) 2829-2834.

- [6] J. Zhou, Y. Gu, P. Fei, W. Mai, Y. Gao, R. Yang, G. Bao, Z.L. Wang, Nano Lett, 8 (2008) 3035-3040.

- [7] Y. Zhang, Y. Liu, Z.L. Wang, Adv Mater, 23 (2011) 3004-3013.

- [8] R. Yu, W. Wu, C. Pan, Z. Wang, Y. Ding, Z.L. Wang, Adv Mater, 27 (2015) 940-947.

- [9] X. Cao, C. Xia, H. Guo, L. Tao, J. Yang, W. Ning, L.W. Zhong, Acs Nano, 10 (2016) 8038.

- [10] J.M. Wu, C.Y. Chen, Y. Zhang, K.H. Chen, Y. Yang, Y. Hu, J.H. He, Z.L. Wang, Acs Nano, 6 (2012) 4369-4374.

- [11] W. Han, Y. Zhou, Y. Zhang, C.Y. Chen, L. Lin, X. Wang, S. Wang, Z.L. Wang, ACS Nano, 6 (2012) 3760-3766.

- [12] Q. Yang, W. Wang, S. Xu, Z.L. Wang, Nano Letters, 11 (2011) 4012-4017.

- [13] X. Wang, W. Peng, R. Yu, H. Zou, Y. Dai, Y. Zi, C. Wu, S. Li, Z.L. Wang, Nano Letters, 17 (2017) 3718.

- [14] D.Q. Zheng, Z.M. Zhao, R. Huang, J.H. Nie, L.J. Li, Y. Zhang, Nano Energy, 32 (2017) 448-453.

- [15] W. Wu, X. Wen, Z.L. Wang, Science, 340 (2013) 952-957.

- [16] C. Pan, L. Dong, G. Zhu, S. Niu, R. Yu, Q. Yang, Y. Liu, Z.L. Wang, Nature Photonics, 7 (2013) 752-758.

- [17] H. Wang, P.P. Mercier, Sci Rep, 7 (2017) 4427.

- [18] Ü. Özgür, Y.I. Alivov, C. Liu, A. Teke, M.A. Reshchikov, S. Doğan, V. Avrutin, S.J. Cho, H. Morkoç, Journal of Applied Physics, 98 (2005) 11-11.

- [19] O. Ambacher, B. Foutz, J. Smart, J.R. Shealy, N.G. Weimann, K. Chu, M. Murphy, A.J. Sierakowski, W.J. Schaff, L.F. Eastman, R. Dimitrov, A. Mitchell, M. Stutzmann, Journal of Applied Physics, 87 (2000) 334-344.

- [20] R.H. Walden, IEEE Journal on Selected Areas in Communications, 17 (1999) 539-550.

Jiaheng Nie received his B.E. in communication engineering from North China University of Water Resources and Electric Power in 2014. He is now pursuing his M.S. degree under the guidance of Professor Yan Zhang in School of Physical Electronics in UESTC. He is interested in the fields of piezotronics and piezo-phototronics.

Gongwei Hu received his B.S. degree (2014) from China Three Gorges University and M.S. degree in Theoretical Physics (2017) from Lanzhou University. He is currently pursuing the Ph.D degree under the guidance of Professor Yan Zhang in School of Physics in UESTC. His research focuses on the field of functional nanostructures and their physics.

Lijie Li is an associate professor at Swansea University, UK. His research interests are design, modeling, fabrication, and characterization of MEMS, NEMS, sensors and actuators. He is Fellow of IET, and senior member of IEEE.

Yan Zhang is a professor at University of Electronic Science and Technology of China. He received his B. S. degree (1995) and Ph.D degree in Theoretical Physics (2004) from Lanzhou University. Then, he worked as associate Professor (2007) and Professor (2013) of Institute of Theoretical Physics in Lanzhou University. In 2009 he worked as research scientist in the group of Professor Zhong Lin Wang at Georgia Institute of Technology. His research interests include inear 6 self-powered nano/micro system, piezotronic and modeling of nonlinear dynamics of NEMS.

### **Graphical Abstract**

Piezotronic Analog-To-Digital Converter based on strain-gated transistor can be used for sensors and piezotronic logic. The new device design has potential application in strain mapping because the piezotronic transistors provide excellent properties of high sensitivity and lower power consumption.

Figure 1, (a) Schematic diagram of the piezotronics SGTs embedded into a flexible substrate. (b) enlarged graph of four piezotronic ADCs. (c) Circuit symbol and equivalent circuit of a single piezotronic ADC. (d) Circuit diagram of N SGT branches.

Figure 2, Calculated strain sensitivities under a set of external strains for proposed SGT devices with different drain voltage  $V_D$  (a) and (d), different resistors in series connection (b) and (e), and various piezoelectric materials such as ZnO, GaN, and InN (c) and (f).

Figure 3, ADC consisting of SGTs and fixed resistors. (a) schematic circuit. (b) simulated  $I-S_g$  curve. (c) logic truth table.

Figure 4, ADC consisting of SGTs and various resistors. (a) schematic circuit. (b) simulated  $I-S_g$  curve. (c) logic truth table.

Figure 5. ADC configured by using a single piezotronic SGT. (a) schematic diagram. (b) equivalent circuit. (c) simulated logic truth table.

Figure 1

Figure 3

Figure 4

| (c) | Strain (%)  | Α | В     | С   | D   | Output States |

|-----|-------------|---|-------|-----|-----|---------------|

|     | 0.00 - 0.25 | 0 | 0     | 0   | 0   | "00"          |

|     | 0.25 - 0.50 | 0 | 0     | 0   | 1   | "01"          |

|     | 0.50 - 0.75 | 0 | 0     | 1   | 1 ( | "10"          |

|     | 0.75 - 1.00 | 0 | 1     | 1   | 1   | "11"          |

|     | >1.00       | 1 | 1     | 1   | 1   | NA            |

|     | CCCC        |   | Figur | e 5 |     |               |

### **Highlights:**

- 1. SGTs exhibit multiple functions in the single piezotronic transistor, such as voltage converter, comparator, and amplifier.

- 2. Three piezotronic ADC architectures are investigated based on piezotronic SGTs.