| Cronfa - Swansea University Open Access Repository                                                                                                                                                                                          |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                                                                                                                                                                                                                             |  |  |  |  |

| This is an author produced version of a paper published in :                                                                                                                                                                                |  |  |  |  |

| Science of Computer Programming                                                                                                                                                                                                             |  |  |  |  |

| Cronfa URL for this paper:                                                                                                                                                                                                                  |  |  |  |  |

| http://cronfa.swan.ac.uk/Record/cronfa21769                                                                                                                                                                                                 |  |  |  |  |

| Paper:  James, P., Moller, F., Nga Nguyen, H., Roggenbach, M., Schneider, S. & Treharne, H. (2014). On modelling and verifying railway interlockings: Tracking train lengths. <i>Science of Computer Programming</i> , <i>96</i> , 315-336. |  |  |  |  |

| http://dx.doi.org/10.1016/j.scico.2014.04.005                                                                                                                                                                                               |  |  |  |  |

|                                                                                                                                                                                                                                             |  |  |  |  |

|                                                                                                                                                                                                                                             |  |  |  |  |

|                                                                                                                                                                                                                                             |  |  |  |  |

|                                                                                                                                                                                                                                             |  |  |  |  |

|                                                                                                                                                                                                                                             |  |  |  |  |

|                                                                                                                                                                                                                                             |  |  |  |  |

This article is brought to you by Swansea University. Any person downloading material is agreeing to abide by the terms of the repository licence. Authors are personally responsible for adhering to publisher restrictions or conditions. When uploading content they are required to comply with their publisher agreement and the SHERPA RoMEO database to judge whether or not it is copyright safe to add this version of the paper to this repository. http://www.swansea.ac.uk/iss/researchsupport/cronfa-support/

# Techniques for modelling and verifying railway interlockings

Phillip James<sup>1</sup>, Faron Moller<sup>1</sup>, Hoang Nga Nguyen<sup>1</sup>, Markus Roggenbach<sup>1</sup>, Steve Schneider<sup>2</sup>, Helen Treharne<sup>2</sup>

<sup>1</sup> Swansea University, Wales

<sup>2</sup> University of Surrey, England

Received: date / Revised version: date

**Abstract.** We describe a novel framework for modelling railway interlockings which has been developed in conjunction with railway engineers. The modelling language used is CSP||B. Beyond the modelling we present a variety of abstraction techniques which make the analysis of medium to large scale networks feasible. The paper notably introduces a covering technique that allows railway scheme plans to be decomposed into a set of smaller scheme plans. The finitisation and topological abstraction techniques are extended from previous work and are given formal foundations. All three techniques are applicable to other modelling frameworks besides CSP||B. Being able to apply abstractions and simplifications on the domain model before performing model checking is the key strength of our approach. We demonstrate the use of the framework on a real-life, medium size scheme plan.

### 1 Introduction

Formal verification of railway control software has been identified as one of the "grand challenges" of Computer Science [13]. This challenge comes in two parts. The first addresses the question of whether proposed mathematical models faithfully represent the railway domain; verifications must translate to guarantees in the real world. The second addresses the question of how to employ available technologies effectively; analyses must be doable in practice and not just in theory.

In a series of papers [25,24,26,23] we have been developing a new modelling approach for railway interlockings. This work is carried out in conjunction with railway engineers drawn from our industrial partner. By

involving the railway engineers from the start, we benefit twofold: they provide realistic case studies; and—more importantly—they guide the modelling approach, ensuring that it is natural to the working engineer and incorporates all relevant concerns. Our approach thus addresses the first part of the grand challenge.

We base our modelling approach on CSP||B [34], which combines event-based with state-based modelling. This reflects the double nature of railway systems, which involves events such as train movements and—in the interlocking—state based reasoning. In this sense, CSP||B offers the means for the natural modelling approach we strive for. The formal models are, by design, close to the domain models; to the domain expert, this provides traceability and ease of understanding. Our industrial partners can use our modelling approach, and readily recognise it to be fully faithful to their real world concerns.

In addressing the second part of the grand challenge, we face the wider challenge for formal methods of overcoming state space explosion. Having rendered a real-world problem into a modelling language, it remains a mystery in general as to how to decompose a verification problem into tractable pieces whose solutions can be composed together to provide a solution to the initial problem. Our approach is to carry out abstractions at the domain level, thus avoiding the lack of general compositional techniques in modelling languages.

We have developed three abstraction techniques which have proven successful in practice, both in isolation and taken together:

- 1. *finitisation* reduces the number of trains that need to be considered in order to prove safety for an unbounded number of trains;

- 2. covering decomposes the network into a set of subnetworks in a compositional fashion: proving correctness results for the sub-networks suffices to infer the correctness of the whole network; and

3. topological abstraction reduces the number of tracks in the topology of the network, so as to minimise the size and complexity of the network prior to its analysis.

The second abstraction technique is a particular strength of our approach. Winter [38] theorized on the possibility of such compositional proof strategies for the railway domain, but to our knowledge there has since been no practical solution. This is the notable contribution of this paper which has not been presented in our previous work. The other techniques in this paper build upon their presentation in [24]. Firstly, we further reduce the number of trains that need to be considered during analyses. Secondly, we improve upon the topological abstraction technique as a consequence of having more detailed CSP||B models in this paper.

The verification that we focus on in this paper is the safety verification of three safety conditions: collision-freedom, runthrough-freedom and no-derailment. Our verification extends beyond checking the correctness of the configuration data of an interlocking. We address behavioural safety since we concern ourselves with train movements in our CSP||B models. Nonetheless, our modelling abstracts from the realtime behaviour of the interlocking and of the network as a train passes through it.

The paper is organised as follows. In Section 2, we introduce the traditional engineer's view of railway concepts, including a presentation of a complex real-life example which we shall use as a case study. We also outline three safety conditions that we will concentrate on verifying. In Section 3, we outline our approach to verification in general terms independent of any modelling language, as well as then outline a domain-specific modelling language on which we will base our modelling. In Section 5, we present our specific modelling language CSP||B, and apply this language to the railway domain in Section 6.

Having outlined the modelling framework, the next three sections of the paper outline our abstraction techniques: Section 7 presents finitisation, Section 8 presents covering and Section 9 presents topological abstraction. In Section 10, we present experimental results demonstrating the effectiveness of the abstractions. In Section 11, we discuss related approaches to the railway verification problem. Finally, in Section 12, we recap our achievements and outline directions of future research.

#### 2 Railway systems

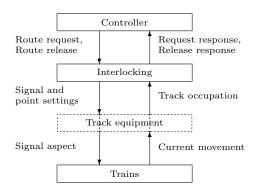

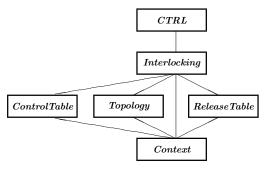

Together with railway engineers, we have developed a common view of the information flow in railways. In physical terms, a railway consists of (at least) the four different components shown in Figure 1.

- The *Controller* selects and releases routes for trains.

Fig. 1: Information flow.

- The Interlocking serves as a safety mechanism with regards to the Controller and, in addition, controls and monitors the Track equipment.

- The *Track equipment* consists of elements such as signals, points, and track circuits. Signals can show the aspects *green* or *red*; points can be in *normal* position (leading trains straight ahead) or in *reverse* position (leading trains to a different line); and track circuits detect if there is a train on a track.

- Finally, Trains have a driver who determines their behaviour.

For the purposes of modelling, we have made the simplification to only consider two aspect signalling, we do not consider the additional aspects of caution or speed limits. We also make the assumption that track equipment reacts instantly and is free of defects. We furthermore assume that trains are shorter than the track segments in the network. In [15], we address the question of how to extend our modelling framework in order to deal with deal with lengths of track segments and trains.

The information flow shown in Figure 1 is as follows: the controller sends a request message to the interlocking to which the interlocking responds; the interlocking sends signalling information to the track equipment and receives information from track sensors on whether a track element is occupied. The interlocking and the trains interact indirectly via the track equipment only. The interlocking serves as the system's clock: in a cycle the status of all the track sensors are read then the interlocking reacts to all of them with one change of state. Routes cannot be in conflict since requests to select and release routes are sequentialised. In our modelling we will abstract away from modelling the track equipment explicitly.

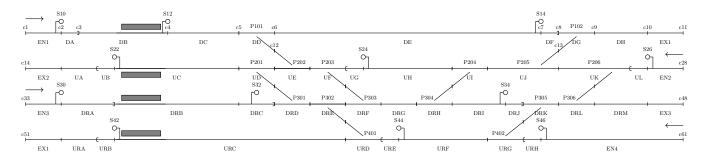

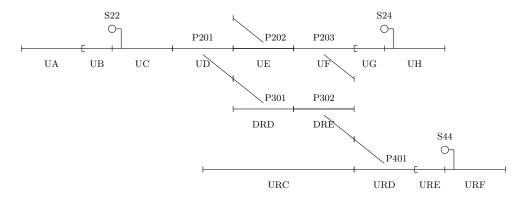

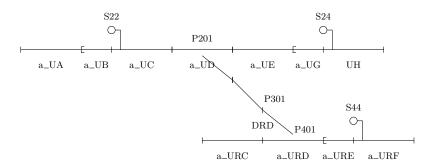

In this paper, we analyse a track layout based on Langley Station, a nontrivial station just to the west of London which is used by over 700,000 people each year [31], and considered to be a medium size station in the UK. Figures 2 and 3 depict the *scheme plan* for the station comprising of a track plan, a control table, and release tables. The track plan is publicly available from [29]; however, as signalling rules are confidential, our control

Fig. 2: Track plan based on Langley Station.

| Route | Normal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Reverse             | Clear                                                                                                                                                                                                                                                            |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R10   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     | DA,DB,DC                                                                                                                                                                                                                                                         |

| R12A  | P101,P202                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     | DC,DD,DE,DF                                                                                                                                                                                                                                                      |

| R12B  | P204,P304,P305                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P101,P202,P203,P303 | DC,DD,UE,UF,DRF,DRG,DRH,DRI,DRJ                                                                                                                                                                                                                                  |

| R14   | P102,P205                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     | DF,DG,DH                                                                                                                                                                                                                                                         |

| R26A  | P204,P205,P206,P304,P306                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                     | UL,UK,UI,UJ,UH,UG                                                                                                                                                                                                                                                |

| R26B  | , , , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | P206,P306,P305,P402 | UL,UK,DRL,DRK,URG,URF,URE                                                                                                                                                                                                                                        |

| R24   | P203,P202,P201,P101,P301                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                     | UG,UF,UE,UD,UC,UB                                                                                                                                                                                                                                                |

| R22   | , , , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     | UB,UA                                                                                                                                                                                                                                                            |

| R30   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     | DRA,DRB,DRC                                                                                                                                                                                                                                                      |

| R32A  | P301,P302,P303,P304,P203,P204,P401                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                     | DRC,DRD,DRE,DRF,DRG,DRH,DRI,DRJ                                                                                                                                                                                                                                  |

| R32B  | P301,P302,P303,P203,P401                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | P204,P205,P102,P304 | DRC,DRD,DRE,DRF,DRG,DRH,UI,UJ,DG,DH                                                                                                                                                                                                                              |

| R34   | P305,P306,P206                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 ' ' '             | DRJ,DRK,DRL,DRM                                                                                                                                                                                                                                                  |

| R46   | P402,P305,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                     | URH,URG,URF,URE                                                                                                                                                                                                                                                  |

| R44A  | P401,P302,P304                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     | URE,URD,URC,URB                                                                                                                                                                                                                                                  |

| R44B  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | P401,P302,P301,P201 | URE,URD,DRE,DRD,UD,UC,UB                                                                                                                                                                                                                                         |

| R42   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     | URB,URA                                                                                                                                                                                                                                                          |

|       | P101         Occupied         P102         Occupied           R12A         DE         R14         DH           R12B         UE         R32B         DH           R24         UD         UD         The control of the con | P201   Occupied     | P202         Occupied         P203         Occupied           R12A         DE         R12B         DRF           R12B         UF         R24         UE           R24         UD         R32A         DRG           R32B         DRG                             |

|       | P204         Occupied           R12B         DRI           R26A         UH           R26B         DRH           R32A         DRI           R32B         UJ             P205         Occupie           R14         DH           R26A         UI           R32B         DG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | P206   Occupied     | P301         Occupied         P302         Occupied           R24         UA         R32A         DRF           R32A         DRF         R32B         DRF           R32B         DRE         R44A         URC           R44B         UD         R44B         DRD |

| P303  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     | ccupied P401 Occupied P402 Occupied                                                                                                                                                                                                                              |

| R32A  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     | UJ R32A DRF R26B URF                                                                                                                                                                                                                                             |

| R32B  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     | DRK R32B DRF R46 URF                                                                                                                                                                                                                                             |

|       | R26B URG R32F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     | DRK R44A URC                                                                                                                                                                                                                                                     |

|       | R32A DRI R34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DRL                 | R44B DRE                                                                                                                                                                                                                                                         |

|       | R32B UI R46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | URF                 |                                                                                                                                                                                                                                                                  |

Fig. 3: Control Table and Release Tables for Langley Station Track Plan.

and release tables are of our own design, though they have been attested by our industrial partners as being realistic.

We explain our modelling approach here with reference to our Langley Station example. In general, we adhere closely to the established principles laid out in [30]. Following the approach of Bjørner [4], we view a track plan as being built from tracks, connectors, signals and points. Each track is associated with two connectors (or three if the track contains a point). Two tracks are attached together if they share a connector. Each track is also associated with a direction consisting of a (directed) pair of their associated connectors (or two pairs if the track contains a point). Thus a pair  $(c_1, c_2)$  in the

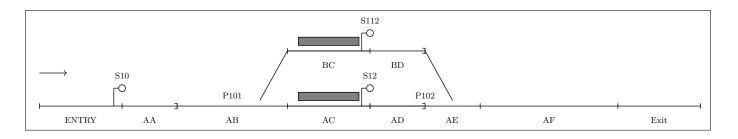

direction of a track indicates that trains can travel on that track from  $c_1$  to  $c_2$ ,  $c_1$  being the connector linking the track to the previous track and  $c_2$  being the connector linking the track to the subsequent track. For example, the Langley station track plan of Figure 2 consists of 49 tracks (e.g., the tracks EN1 and DA), 61 connectors (e.g., the connector  $c_2$  attaching the track EN1 and DA), 16 signals (e.g., S10 and S12), and 16 points (e.g., P101 and P102). Note that the tracks include entry and exit tracks on which trains can "appear" and "disappear" (e.g., EN1, EX1). These two kinds of tracks are specially treated during verification.

An interlocking system gathers train locations, and sends out commands to control signal aspects and point

positions. The control table determines how the station interlocking system sets signals and points. For each route of a signal, there is one row describing the condition under which the signal can show proceed. There are two rows for signal S12: one for route R12A and one for route R12B where, for example, signal S12 can only show proceed when points P101 and P202 are in the normal (straight) position and tracks DC, DD, DE, DF are all clear.

The *normal* direction of a point in a track plan is indicated by an uninterrupted line (from connector  $c_5$  to connector  $c_6$ ), the *reverse* direction with an interrupted line (from connector  $c_5$  to connector  $c_{12}$ ).

Note that we do not assume that trains are equipped with an Automatic Train Protection system which prevents trains from moving over a red light; thus overlaps are needed, e.g., the overlap for Route R12A is DF, and hence DF is included in the control table. Trains are assumed to overrun a red signal by maximally one track. In case that such an overrun has happened, trains are assumed to halt.

The interlocking also allocates *locks* on points to particular route requests to keep them locked in position, and releases such locks when trains have passed. For example, the setting of Route R12A obtains a lock on point P101, and sets it to normal. The lock is released after the train has passed the point. This mechanism allows for the implementation of flank protection. The *release tables* store the relevant track, which is the track after the point.

In this setting, we consider three safety properties:

- 1. *collision-freedom* excludes two trains occupying the same track;

- 2. runthrough-freedom says that whenever a train enters a point, the point is set to cater for this; e.g., when a train travels from track DF to track DG, point P102 is set so that it connects DF and DG (and not UJ and DG);

- 3. *no-derailment* says that whenever a train occupies a point, the point does not move.

The correct design for the control table and release tables is safety-critical: mistakes can lead to a violation of any of the three safety properties.

#### 3 Verification workflow

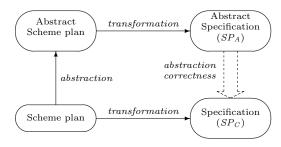

In Figure 4 we depict the verification workflow employed by our approach. Starting from a scheme plan of a railway system represented in a Domain Specific Language (DSL) [21,8] – bottom left – we transform this scheme plan into a concrete specification  $SP_C$  – bottom right. This may be in any of a number of specification languages (e.g., CASL, CSP, Timed CSP, CSP||B, etc.) depending on the approach. However, regardless of the formalism, the specification will inevitably be too complex

Fig. 4: Verification workflow.

for analysis. To remedy this, some form of abstraction is applied to the scheme plan to produce an abstract scheme plan – top left – which is then transformed into an abstract specification  $SP_A$  – top right. With appropriate abstraction correctness results, verification proofs carried out on the abstract specification  $SP_A$  imply the relevant correctness of the concrete specification  $SP_C$ . For example, we have used this approach with topological abstractions in the context of CASL [14] and CSP||B [24]; with a covering abstraction in the context of CSP [22]; and with a finitisation abstraction in the context of Timed CSP [12].

#### 4 A railway DSL

Here, we present a general (mathematical) model of railway networks inspired by the work of Bjørner [4]. We implemented this model in our tool OnTrack [17] which also includes an automated transformation of this model into a CSP||B specification.

A railway network is provided by a scheme plan SP = (Top, CT, RTs) which is comprised of a track plan Top defining the topology of the railway network; a control table CT; and a set RTs of release tables. Note that our model is a loose specification of a railway scheme plan. For our purposes, this under-specification has proven to be sufficient.

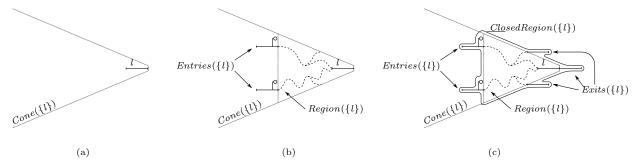

### 4.1 Topology

Let Track and Point denote two disjoint, finite sets of tracks and points, respectively. Tracks and points are collectively referred to as units, and we let Unit = Track $\forall$  Point. There is a set Connector whose elements serve as glue between nodes. A track t, having two endpoints, has two distinct connectors whereas a point p, having three endpoints, has three distinct connectors; we write connectors(u) to denote the set of all connectors of a unit u. A pair  $(c_1, c_2) \in Connector \times Connector$  indicates that a train can travel on a unit u from  $c_1$  to  $c_2$ , where  $c_1, c_2 \in connectors(u)$ . In our setting, a track t can be passed in one direction only; in contrast, a point p is associated with two directions where opposing directions and movement between two specific branches are

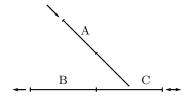

Fig. 5: A point example.

excluded, e.g. in Figure 2 movement between connector  $c_6$  and  $c_{12}$  is not permitted. The two positions that a point can have are called *normal* and *reverse* where  $directions(p) = normal(p) \uplus reverse(p)$ . The direction of a unit can be read as the "intended use" of the unit, which the signal engineer provides when designing the routes, the control table, and release tables. Given a direction  $d = (c_1, c_2) \in directions(t)$  of a track or point t, we denote  $from(d) = c_1$ ,  $to(d) = c_2$ .

A path  $P = \langle (u_1, d_1), \dots, (u_k, d_k) \rangle$ ,  $k \geq 1$ , in a rail-way topology is a non-empty sequence of units and their directions without direct repetitions:  $to(d_i) = from(d_{i+1})$  and  $u_i \neq u_{i+1}$  for all  $1 \leq i < k$ . As usual,  $hd(P) = u_1$  and  $last(P) = u_k$ , and  $u \in P$  if  $u = u_i$  for some  $1 \leq i \leq k$ . When the connectors are clear, we also write  $\langle u_1, \dots, u_k \rangle$  for P.

Note that the composition of two paths is not necessarily a path as direct repetitions are excluded. A typical example is shown in Figure 5. Here,  $\langle A, C \rangle$  is a path and  $\langle C, B \rangle$  is a path, however  $\langle A, C, C, B \rangle$  is not a path. Note however that any non-empty subsequence of a path is a path.

For convenience, we define two functions successor: Unit  $\to \wp(\mathsf{Unit})$  and predecessor: Unit  $\to \wp(\mathsf{Unit})$  as follows:

- $successor(u) = \{x \in Unit \mid \exists c_1, c_2, c_3 \in Connector : \langle (u, (c_1, c_2)), (x, (c_2, c_3)) \rangle \text{ is a path} \}, \text{ and}$

- $predecessor(u) = \{x \in Unit \mid \exists c_1, c_2, c_3 \in Connector : \langle (x, (c_1, c_2)), (u, (c_2, c_3)) \rangle \text{ is a path} \}.$

Units without predecessors are called entries, units without successors are called exits. In the context of this paper, we consider only track plans where entries and exits are tracks, and denote the set of entry and exit tracks as

$\begin{array}{l} - \ \mathsf{Entry} = \{t \in \mathsf{Track} \mid predecessor(t) = \emptyset\} \ \mathrm{and} \\ - \ \mathsf{Exit} = \{t \in \mathsf{Track} \mid successor(t) = \emptyset\}. \end{array}$

We assume a set Signal of signals, along with a labelling function signalAt: Signal  $\rightarrow$  Track indicating tracks at which signals are placed. Each track may be labelled by at most one signal: for each  $t \in \text{Track}$ , signalAt(s) = t for at most one  $s \in \text{Signal}$ . Signals are placed at the end of a track in order to protect the successor track. We require that there is a signal at every entry track. Without such an entry signal, trains could unrestrictedly enter the scheme plan. This would cause collision on the successor of an entry track. Note that the typing of the

Fig. 6: An illustration of the route definition.

function *signalAt* ensures that signals are never placed at a point – which follows standard practice in railway engineering.

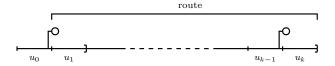

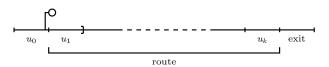

As we deal with open railway topologies, we need to give two different definitions of what a route is: the first definition caters for the case in which the route is completely within the railway topology, while the second definition caters for the case in which a route ends at the border of the topology – see Figure 6. A path  $r = \langle u_1, \ldots, u_k \rangle$  is a topological route if one of the following holds:

- there is a unit  $u_0$  such that

$$\langle u_0, u_1, \ldots, u_k \rangle$$

is a path in which  $u_0$  and  $u_{k-1}$  are labelled with signals but there are no signals on  $u_1, \ldots, u_{k-2}$ . In this case,  $u_k$  is called the *overlap* of r; or

- there are units  $u_0$  and  $u_{k+1}$  such that

$$\langle u_0, u_1, \ldots, u_k, u_{k+1} \rangle$$

is a path,  $u_0$  is labelled with a signal, there are no signals on  $u_1, \ldots, u_k$ , and  $u_{k+1}$  is an exit track.

In both cases, we define  $topoUnits(r) = \{u_1, \ldots, u_k\}$  and topoSignal(r) = s where  $signalAt(s) = u_0$ . Finally, we let TopoRoute denote the set of all topological routes in the railway topology, so that topoUnits: TopoRoute  $\rightarrow \wp(Unit)$  and topoSignal: TopoRoute  $\rightarrow$  Signal.

#### 4.2 Control table

The control table determines the logic for controlling signals and points in the railway network. It specifies conditions when routes can be set which effectively leads to the control of signals' aspects and of points' positions.

Let Route be a set of route names and topoRoute: Route  $\rightarrow$  TopoRoute a function associating topological routes to route names. The function topoRoute is not necessarily surjective as there can be topological routes which a signaller cannot control. E.g., in Figure 3, the control table does not include a route corresponding to the topological route in Figure 2 from the signal S12 to

the exit track EX1 – from track DB down to track DRG (points P101, P202, P203 and P303 all in reverse position) and then again up to track DH (points P304, P204, P205 and P102 all in reverse position). We allow for several entries in the control table that are associated with one topological route. The function  $signal: \mathsf{Route} \to \mathsf{Signal}$  gives the entry signal of the corresponding topological route, i.e., signal(r) = topoSignal(topoRoute(r)). The function  $units: \mathsf{Route} \to \wp(\mathsf{Unit})$  gives the set of units of the corresponding topological route, i.e.,

```

units(r) = topoUnits(topoRoute(r)).

```

The control table specifies, for each route  $r \in \mathsf{Route}$ : a set clear(r) of tracks and points to be clear; a set normal(r) of points to be in the normal position; and a set reverse(r) of points to be in the reverse position. Informally, when all units in clear(r) are unoccupied, all points in normal(r) are in the normal position, and all points in reverse(r) are in the reverse position, route r can be set which effectively changes the aspect of signal(r) to "proceed".